Новая плата совмещенной обработки сигналов DSP и FPGA с процессором NIOS2 - купить

Специальная цена от 8871 руб.*

Категория товара: Интегральные схемы

История изменения цены

*Внимание! Указанная цена 8871 уже могла изменится, перед тем как купить данный товар перейдите на страницу продавца и проверьте актуальную стоимость.

| Месяц | Мин. | Макс. | Цена |

|---|---|---|---|

| 17.02.2026 | 11266.92 | 11491.47 | 11378.5 руб. |

| 17.01.2026 | 9137.0 | 9320.31 | 9228.5 руб. |

| 17.12.2025 | 11089.19 | 11311.76 | 11200 руб. |

| 17.11.2025 | 11000.64 | 11220.7 | 11110 руб. |

| 17.10.2025 | 8782.97 | 8958.55 | 8870 руб. |

| 17.09.2025 | 10823.68 | 11039.62 | 10931 руб. |

| 17.08.2025 | 10734.81 | 10949.35 | 10841.5 руб. |

| 17.07.2025 | 10645.53 | 10858.73 | 10751.5 руб. |

Купить DSP2812 Новая плата DSP + FPGA NIOS2 |

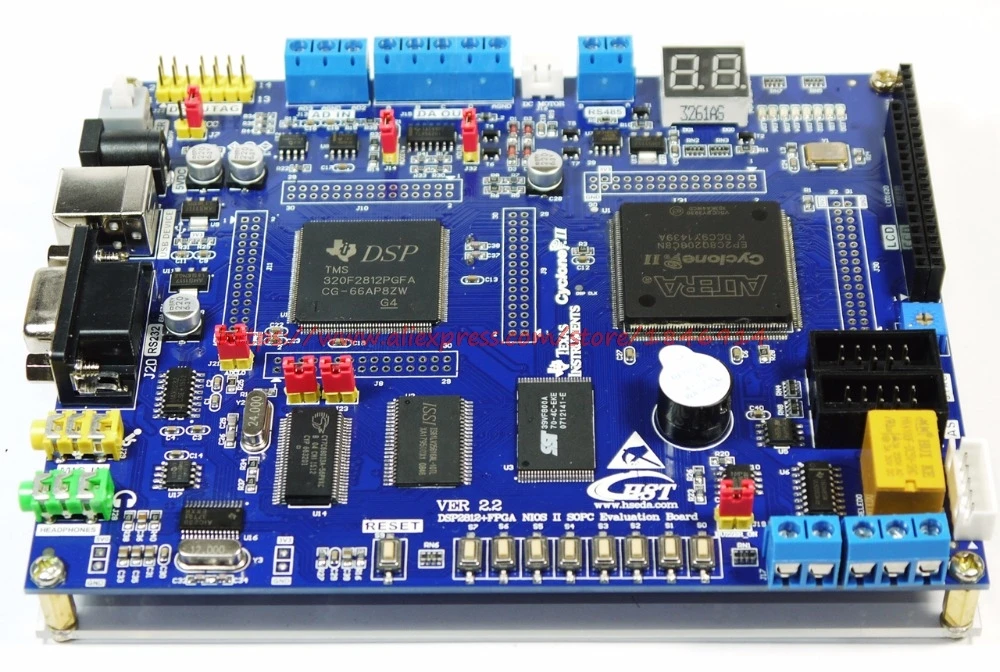

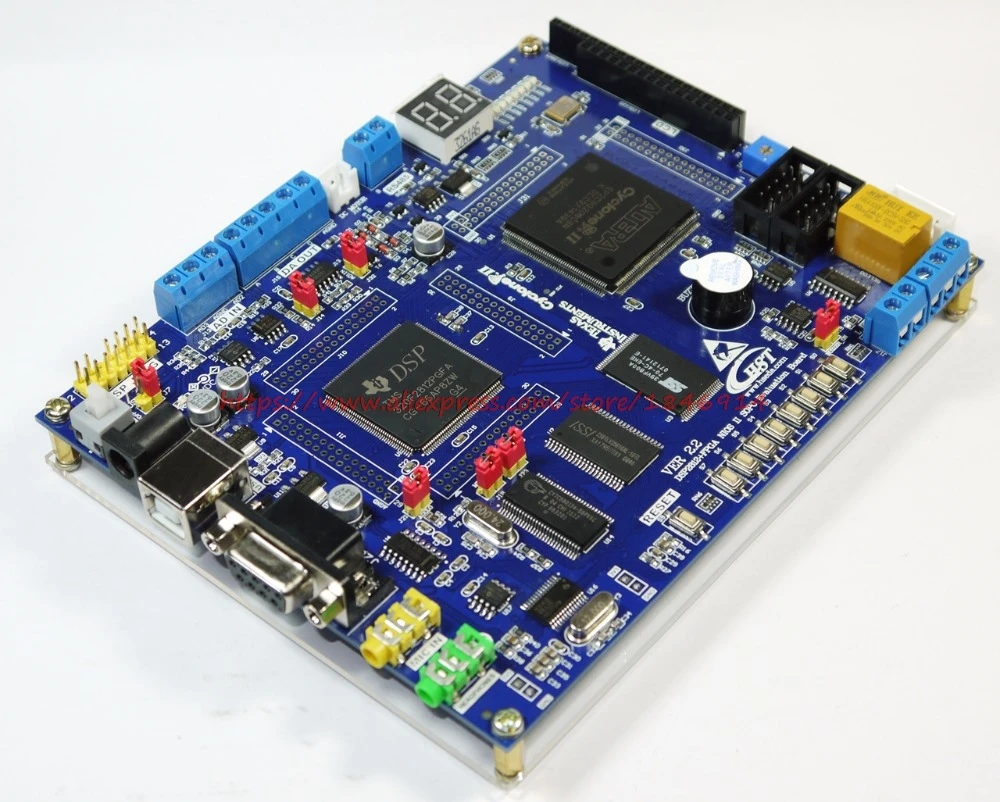

Этот набор основан на платформе обучения TMS320F2812 + EP2C8Q208C8 DSP + FPGA + NIOS, дает полную игру TMS320F2812 и гибкость ALTERA CYCLONE II и мощные функции. Руководство пользователя по разработке комплекта легко понять, легко использовать большое количество исходного кода (DSP И FPGA 2 части). Мы предоставляем пользователям полный FPGA IP ядро, система через IP ядро системы распределения ресурсов и подключения, пользователь может быть сокращен или добавить функциональность по мере необходимости. Потому что наши периферийные устройства соединены FPGA и DSP, преобразование уровня, изоляция шины и третейские и другие передовые технологии, поэтому использование очень удобное и гибкое, простое. Из-за использования такого вида системы структуры, поэтому Операция является чрезвычайно стабильной и надежной и может быть скорректирована в соответствии с требованиями высокой скорости, ток вождения каждого порта ввода/вывода задержки, стандарты входного и выходного уровня, Может полностью использовать большое количество CycloneII IP nuclear и PLL высокоскоростной, высокая стабильность приложения DSP + FPGA, вы также можете использовать ALTERA DSP builder generation one или более DSP IP core appliance system, это будет составлять многоядерный процессор. Эти ресурсы недоступны для general CPLD. Эта структура обеспечивает полную гибкость FPGA, а также высокую производительность и богатые ресурсы TMS320F2812. Плата разработки разработана старшим инженером в соответствии с спецификацией высокочастотной системы проводки, которая полностью принимает во внимание проблемы системы против помех и петли. Является первым выбором для начинающих и занимается разработкой научно-исследовательских работников для обучения DSP F2812 и FPGA.

Этот набор основан на платформе обучения TMS320F2812 + EP2C8Q208C8 DSP + FPGA + NIOS, дает полную игру TMS320F2812 и гибкость ALTERA CYCLONE II и мощные функции. Руководство пользователя по разработке комплекта легко понять, легко использовать большое количество исходного кода (DSP И FPGA 2 части). Мы предоставляем пользователям полный FPGA IP ядро, система через IP ядро системы распределения ресурсов и подключения, пользователь может быть сокращен или добавить функциональность по мере необходимости. Потому что наши периферийные устройства соединены FPGA и DSP, преобразование уровня, изоляция шины и третейские и другие передовые технологии, поэтому использование очень удобное и гибкое, простое. Из-за использования такого вида системы структуры, поэтому Операция является чрезвычайно стабильной и надежной и может быть скорректирована в соответствии с требованиями высокой скорости, ток вождения каждого порта ввода/вывода задержки, стандарты входного и выходного уровня, Может полностью использовать большое количество CycloneII IP nuclear и PLL высокоскоростной, высокая стабильность приложения DSP + FPGA, вы также можете использовать ALTERA DSP builder generation one или более DSP IP core appliance system, это будет составлять многоядерный процессор. Эти ресурсы недоступны для general CPLD. Эта структура обеспечивает полную гибкость FPGA, а также высокую производительность и богатые ресурсы TMS320F2812. Плата разработки разработана старшим инженером в соответствии с спецификацией высокочастотной системы проводки, которая полностью принимает во внимание проблемы системы против помех и петли. Является первым выбором для начинающих и занимается разработкой научно-исследовательских работников для обучения DSP F2812 и FPGA.

Вспомогательная информация и соответствующее программное обеспечение для разработки

Полная схема (формат PDF и PCB полностью соответствуют), ряд практичных интерфейсов для захвата приложения;

Все эксперименты содержат исходный код языка C, есть подробные китайские Примечания;

Методы и инструменты онлайн-вспышки для закрепления собственных процедур пользователя;

Руководство по чипу: предоставьте все чипы на макетной плате;

Отправьте оригинальную среду разработки TI DSP CCS3.3;

Предоставляем драйвер симулятора и другие обучающие материалы, связанные с DSP книгами CD;

Даем Acrobat reader, Bushound USB bus программное обеспечение для мониторинга, Sscom серийный помощник отладки инструменты отладки;

Дать Altera скачать линейную схему;

Мини ЖК-шрифт программного обеспечения;

Представленный TCP/IP объем протокола: Объем 1 ~ 3;

Документ спецификации USB;

Документ спецификации CAN2.0;

Предоставьте U дисковую системную документацию;

Представлено системное документирование FAT16, FAT32;

Подарочная UCOS-II на источнике трансплантации F2812;

Как FFT, FIR и т. Д.;

TI посылка с полным чипом;

Руководство пользователя: Очень подробное описание, включая анализ цепи, код, руководство по быстрому запуску CCS2000;

QUARTUS 11,0 + NIOS IDE 11 development environment полностью треснутая версия II.

Коллекция программ VHDL

VHDL учебник

Чехлы VERILOG рутинные 135

Учебник VERILOG

Учебник DSPbuilder

Отправить серийный порт мониторинга программного обеспечения, разработка RS232 essential

Разработка программного обеспечения извлечения шрифта требуемые процедуры ЖК-дисплея

USB2.0 главная компьютерная программа и ее источник

Полная система распределения ресурсов FPGA IP ядро и его источник.

Большое количество полных учебников по разработке NIOS. Включая DSP, EDA, SOPC видео-учебник. Позволяет легко осваивать DSP, FPGA, SOPC системную разработку.

Вспомогательная информация и соответствующее программное обеспечение для разработки

Полная схема (формат PDF и PCB полностью соответствуют), ряд практичных интерфейсов для захвата приложения;

Все эксперименты содержат исходный код языка C, есть подробные китайские Примечания;

Методы и инструменты онлайн-вспышки для закрепления собственных процедур пользователя;

Руководство по чипу: предоставьте все чипы на макетной плате;

Отправьте оригинальную среду разработки TI DSP CCS3.3;

Предоставляем драйвер симулятора и другие обучающие материалы, связанные с DSP книгами CD;

Даем Acrobat reader, Bushound USB bus программное обеспечение для мониторинга, Sscom серийный помощник отладки инструменты отладки;

Дать Altera скачать линейную схему;

Мини ЖК-шрифт программного обеспечения;

Представленный TCP/IP объем протокола: Объем 1 ~ 3;

Документ спецификации USB;

Документ спецификации CAN2.0;

Предоставьте U дисковую системную документацию;

Представлено системное документирование FAT16, FAT32;

Подарочная UCOS-II на источнике трансплантации F2812;

Как FFT, FIR и т. Д.;

TI посылка с полным чипом;

Руководство пользователя: Очень подробное описание, включая анализ цепи, код, руководство по быстрому запуску CCS2000;

QUARTUS 11,0 + NIOS IDE 11 development environment полностью треснутая версия II.

Коллекция программ VHDL

VHDL учебник

Чехлы VERILOG рутинные 135

Учебник VERILOG

Учебник DSPbuilder

Отправить серийный порт мониторинга программного обеспечения, разработка RS232 essential

Разработка программного обеспечения извлечения шрифта требуемые процедуры ЖК-дисплея

USB2.0 главная компьютерная программа и ее источник

Полная система распределения ресурсов FPGA IP ядро и его источник.

Большое количество полных учебников по разработке NIOS. Включая DSP, EDA, SOPC видео-учебник. Позволяет легко осваивать DSP, FPGA, SOPC системную разработку.

Полный драйвер FPGA IP и его источник

Завершите системную логику и системную интеграцию, распределение ресурсов, пользователи могут быть собраны в соответствии с их собственными потребностями и их применением, поэтому системные ресурсы через соединение FPGA имеют соответствующий адрес чтения и записи, И предоставить полный SDRAM IP core,

Пользователь может использовать систему хранения данных большой емкости, компания предоставит пользователям высокоскоростное AD/DA более дешевое TFT расширение, ЖК-расширение, оптопара высокого тока I/O Модуль обратите внимание на веб-сайт Huasheng EDA.

Область применения

DSP + FPGA + EDA обучение

Управление промышленной автоматизации

UPS, управление двигателем

Цифровая фильтрация и вибрационный анализ

Управление переменной частотой

Список доставки! (улучшенная конфигурация)

DSP2812 + FPGA VER2.0 основная плата

5В/1A импульсный источник питания

1 линии связи USB2.0

1 RS232 линии связи

LCD 1602 LCD 1

XDS100 V1 USB DSP интерфейс симулятор 1

Двигатель постоянного тока 1

Шаговый двигатель 1

USB BLASTER линия загрузки (VE R.C) 1 (FPGA скачать отладчик);

DuPont line (2,0 мм поворот 2,54 мм 5 пар) 10

Шесть углов 4 столбов

3 40 игла 2,0 мм двухрядная игла 3

Акриловая пластина 1

Поддержка данных CD DVD 3

Полный драйвер FPGA IP и его источник

Завершите системную логику и системную интеграцию, распределение ресурсов, пользователи могут быть собраны в соответствии с их собственными потребностями и их применением, поэтому системные ресурсы через соединение FPGA имеют соответствующий адрес чтения и записи, И предоставить полный SDRAM IP core,

Пользователь может использовать систему хранения данных большой емкости, компания предоставит пользователям высокоскоростное AD/DA более дешевое TFT расширение, ЖК-расширение, оптопара высокого тока I/O Модуль обратите внимание на веб-сайт Huasheng EDA.

Область применения

DSP + FPGA + EDA обучение

Управление промышленной автоматизации

UPS, управление двигателем

Цифровая фильтрация и вибрационный анализ

Управление переменной частотой

Список доставки! (улучшенная конфигурация)

DSP2812 + FPGA VER2.0 основная плата

5В/1A импульсный источник питания

1 линии связи USB2.0

1 RS232 линии связи

LCD 1602 LCD 1

XDS100 V1 USB DSP интерфейс симулятор 1

Двигатель постоянного тока 1

Шаговый двигатель 1

USB BLASTER линия загрузки (VE R.C) 1 (FPGA скачать отладчик);

DuPont line (2,0 мм поворот 2,54 мм 5 пар) 10

Шесть углов 4 столбов

3 40 игла 2,0 мм двухрядная игла 3

Акриловая пластина 1

Поддержка данных CD DVD 3

Отзывы о Новая плата совмещенной обработки сигналов DSP и FPGA с процессором NIOS2

Здесь вы можете оставить свой отзыв о данном товаре.

Отзывы ( 0 )

Сначала новые

Сначала старые

Сначала лучшие

Отправить

Загрузить

Ссылка

Сообщение:

Загрузить

Ссылка

ССЫЛКА НА ИЗОБРАЖЕНИЕ

Загружено по ссылке